# ple VCPL (VCXO)

# Pletronic, Inc.

19013 36th Ave. West • Suite H • Lynnwood, WA 98036, USA

- HIGH-FREQUENCY VCXO IN THRU-HOLE OR SMD METAL PACKAGE

- PHASED-LOCK LOOP CIRCUIT (PLLC) USED

- 300 pS RMS MAXIMUM JITTER

# STANDARD SPECIFICATIONS:

| Frequency Range                                  | 60.000 - 160.000 MHz                                                        |  |  |  |

|--------------------------------------------------|-----------------------------------------------------------------------------|--|--|--|

|                                                  | (Consult factory for specific available frequencies)                        |  |  |  |

| Operating Temperature Range                      | 0 - 70°C is standard, but can be extended to – 40 to +85°C                  |  |  |  |

| Frequency Stability over Operating               | 100 DDM is standard but 115, 25, 50 ppm also sysilable                      |  |  |  |

| Temperature Range and Supply Voltage             | $\pm$ 100 PPM is standard but $\pm$ 15, 25, 50 ppm also available.          |  |  |  |

| Aging                                            | 3 PPM first year, 1 PPM per year thereafter at $25^{\circ}C \pm 5^{\circ}C$ |  |  |  |

| Input Voltage                                    | $5 V \pm 5\%$ Volt is standard but 3.3 V $\pm$ 5% also available            |  |  |  |

| Output Logic Level                               | HCMOS/TTL Compatible                                                        |  |  |  |

| Input Current (Icc) & Rise & Fall Time (Tr & Tf) | Depends on frequency. See table on next page.                               |  |  |  |

| Output Load                                      | CMOS Load + 15 pF                                                           |  |  |  |

| Control Voltage Range                            | $2.5V \pm 2.0V$ for Vcc = 5.0V, 1.65V $\pm$ 1.32V for Vcc = 3.3V            |  |  |  |

| Frequency Deviation (Pullability) over the       | 1.25 EQ. 100, 150, 200, and 200 DBM subjects                                |  |  |  |

| Control Voltage Range                            | $\pm$ 25, 50, 100, 150, 200, and 300 PPM available.                         |  |  |  |

| Linearity                                        | ± 10%                                                                       |  |  |  |

| Packaging                                        | 20 parts per tube, SMD: Tape and Reel TBD                                   |  |  |  |

### PART NUMBERING GUIDE:

- The Pletronics part number for a VCPL VCXO consists of the following 6 elements:

- 1. Model Number (Voltage): VCPL = 5V 3VCPL = 3.3V

### 2. Frequency Stability:

VCPL<u>15</u>: ±15 PPM VCPL<u>25</u>: ±25 PPM VCPL<u>50</u>: ±50 PPM VCPL<u>100</u>: ±100 PPM

## 3. Operating Temperature Range:

VCPL100<u>A</u>: 0 to +50° VCPL100<u>C</u>: -10 to +70°C VCPL100<u>E</u>: -30 to +75°C VCPL100<u>B</u>: 0 to +70°C VCPL100<u>D</u>:-20 to +75°C VCPL100<u>F</u>:-40 to +85°C

#### 4. Frequency Deviation over Control Voltage Range: VCPI 100AT: +25 PPM VCPI 100AV: +50 PPM

| VOFLIUUA <u>I</u> . ±23 FFIVI | V OF LIVUA <u>V</u> . ±30 F F M |

|-------------------------------|---------------------------------|

| VCPL100A <u>W</u> : ±100 PPM  | VCPL100AX: ±150 PPM             |

| VCPL100A <u>Y</u> : ±200 PPM  | VCPL100A <u>Z:</u> ±300 PPM     |

- 5. Frequency of Operation in MHz

- 6. Optional Surface Mount Configuration SMD

EXAMPLE: VCPL100CW-60.000 MHz, VCPL50DZ-60.000 MHz-SMD, 3VCPL15FT-60.000 MHz

■ When customer's requirements are non-standard, a special engineering part number will be assigned.

(continued)

# VCPL VCXO

# Input Current and Rise & Fall Time with 15 pF CMOS Load

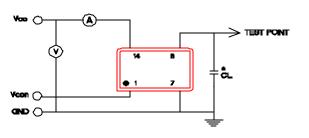

# **Recommended Test Circuit**

| Freq. Range<br>(MHz) | lcc (mA) |      | Tr & Tf (nS) |     |

|----------------------|----------|------|--------------|-----|

|                      | Тур      | Max  | Тур          | Max |

| 60.000 - 100.000     | 25.0     | 30.0 | 1.5          | 2.5 |

| 100.001 - 120.000    | 30.0     | 35.0 | 1.5          | 2.5 |

| 120.001 - 140.000    | 35.0     | 40.0 | 1.5          | 2.5 |

| 140.001 – 160.000    | 40.0     | 45.0 | 1.5          | 2.5 |

\*CL (Capacitive Load): Includes the input capacitance of oscilloscope

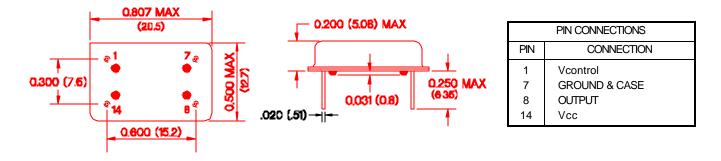

# Package Outline (Not to Scale):

#### SMD OUTLINE .247 (6.26) RECOMMENDED LAND PATTERN OPTIONS MAX PAD OPTION 2 PAD OPTION 3 PAD OPTION 1 0.82 (20.8) MAX 0.20 (5.1) 0.60 (15.2) 0.767 (19.5) 0.60 (15.2)8 8 14 14 0.56 MAX ÔE 8 (14.2) 0.07 (1.8) TYP 0.52 (13.2) 0.30 (7.6) 0.30 (7.6) 7 🛙 h 7 0.12 (3.1) TYP 1 0.20 (5.1) TYP

**INCHES (MILLIMETERS)**

January 2000